March 9, 2018

#### RTL DESIGN WITH ARX

#### IMPLEMENTATION OF DIGITAL SIGNAL **PROCESSING**

Sabih H. Gerez University of Twente

© Sabih H. Gerez, University of Twente, The Netherlands

March 9, 2018

RTL DESIGN WITH ARX

# **GENERAL PURPOSE VS. DOMAIN-**SPECIFIC DESIGN LANGUAGES

- Should one adopt (and adapt) existing programming languages for the design of parallel embedded systems, signal processing systems?

- Yes, because:

IMPLEMENTATION OF DSP

- This alleviates the burden of making new compilers, debuggers, etc.

- No. because:

- One wants to model only the semantics of some domain and wants to keep the language clean of peculiarities of the host language.

# RTL DESIGN WITH ARX

#### OUTLINE

- Design languages

- Arx motivation and alternatives

- Main features of Arx

- Arx language elements

- Components and functions

- Data types

- Statements

- Code generation and simulation

IMPLEMENTATION OF DSP RTL DESIGN WITH ARX

## ON LEARNING NEW LANGUAGES

© Sabih H. Gerez, University of Twente, The Netherlands

- Reusing an existing language for specific modeling domains is not necessarily a good idea.

- What matters, is mastering the semantics of the domain.

- Learning to think in the paradigms of the domain takes much longer than learning a new programming language.

- It is e.g. a mistake to think that one convert a C programmer into a hardware designer by providing her with a tool that synthesizes hardware from C.

Edwards, S.A., The Challenges of Synthesizing Hardware from C-Like Languages, IEEE Design and Test of Computers, pp. 375-385, (September/October 2006).

March 9, 2018

#### THE LANGUAGE SUBSET ISSUE

- When an existing language is used for describing models in a new language, one is confronted with the fact that not all language constructs make sense in the application domain.

- One necessarily needs to isolate a language subset that should be used.

- This is true for e.g. C.

- But also for e.g. VHDL, originally a simulation language, later used for synthesis.

© Sabih H. Gerez, University of Twente, The Netherlands

IMPLEMENTATION OF DSP RTL DESIGN WITH ARX

March 9, 2018

#### **DATA-FLOW LANGUAGES**

- They have the single-assignment property: a variable is only assigned a value once.

- This means that, after conversion into a DFG, the variable can be associated to the output of a single vertex.

- · Because of single assignment, ordering of statements is not relevant.

- Think also of VHDL: a process should in principle write a signal only once (unless it contains wait statements).

- They can have syntactic support for typical data-flow elements such as the delay node.

March 9, 2018

**DOMAIN-SPECIFIC LANGUAGES**

- Languages specifically designed for well-defined, constrained, modeling are called domain-specific languages.

- No design mistakes due to subset violations: all language constructions are meaningful in domain.

- Tools such as parsers can be kept simple as they only need to deal with a small language rather than a large and complex one.

© Sabih H. Gerez, University of Twente, The Netherlands

IMPLEMENTATION OF DSP

March 9, 2018

RTL DESIGN WITH ARX

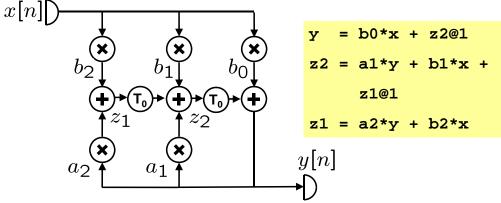

# **DATA-FLOW LANGUAGE EXAMPLE: SILAGE**

Hilfinger, P.N., "A High-Level Language and Silicon Compiler for Digital Signal Processing", Custom Integrated Circuit Conference, pp. 213-216, (1985).

#### DATA FLOW IN C

- Voluntarily stick to single-assignment code.

- Use static variables for delay elements and read these values before writing them.

```

T out sec(T in x) {

static T reg z1 = 0;

static T reg z2 = 0; ...

Can this go

y = b0*x + z2;

wrong?

z2 \text{ nxt} = a1*y + b1*x + z1;

z1 nxt = a2*y + b2*x;

z2 = z2_nxt; z1 = z1_nxt; // register update

return(y);

```

IMPLEMENTATION OF DSP

RTL DESIGN WITH ARX

March 9, 2018

11

#### C-BASED HARDWARE DESIGN

© Sabih H. Gerez, University of Twente, The Netherlands

- Arguments in favor of C-based design:

- Everybody knows C; we don't want to teach new languages.

- Lots of legacy C code.

- High execution speed.

- Many commercial products based on translation from C/C++/SystemC including:

- Catapult (Calypto part of Mentor Graphics)

- Stratus (Cadence, replaces C-to-Silicon and Cynthesizer)

- Synphony C Compiler (Synopsys, formerly Synfora PICO)

- Vivado (Xilinx, formerly AutoESL)

- Intel HLS Compiler (Intel/Altera, front-end to Platform Designer/Quartus)

- CyberWorkBench (NEC System Technologies)

March 9, 2018

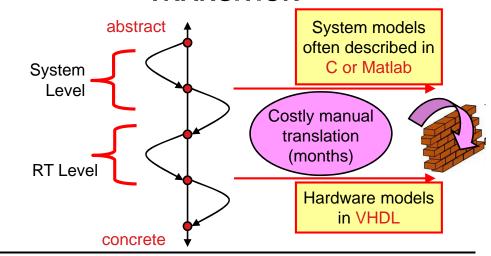

# PRACTICE IN SYSTEM-LEVEL-TO-RTL **TRANSITION**

© Sabih H. Gerez, University of Twente, The Netherlands

IMPLEMENTATION OF DSP

March 9, 2018

12

RTL DESIGN WITH ARX

#### **GRAPHICAL DESIGN ENTRY**

- Many solutions based on dedicated blocksets to be used in Simulink:

- Mathwork's HDL Coder (from graphics and text source)

- Synphony Model Compiler (Synopsys)

- Xilinx System Generator for DSP

- Intel/Altera DSP Builder

- Graphical design entry can be cumbersome compared to textbased entry:

- One does not always want to instantiate an adder for every addition, a multiplexer for every if-statement, etc.

Functional

Bit-true

Bit-true and

clock-cycle-true

# DOMAIN-SPECIFIC DESIGN LANGUAGES

- All language constructs make sense in domain:

- Entire language is synthesizable.

- Designer does not need to bother about allowed subsets.

- Straightforward language constructions:

- Improve designer efficiency.

- Lead to elegant designs.

- Examples:

- Bluespec (commercial)

- GEZEL (university tool)

© Sabih H. Gerez, University of Twente, The Netherlands

IMPLEMENTATION OF DSP

15

RTL DESIGN WITH ARX

March 9, 2018

#### **ARX EXAMPLE**

# LANGUAGE Domain-specific RTL language: Arx One language (Arx) for multiple levels. Developed at University of Twente. Arx eliminates manual translation from C to VHDL!

Correct by construction.

C++ Verification with C-based

simulation

VHDL RTL synthesis

© Sabih H. Gerez, University of Twente, The Netherlands

generator

generator

UT.

IMPLEMENTATION OF DSP

March 9, 2018

16

RTL DESIGN WITH ARX

Waron 0, 20

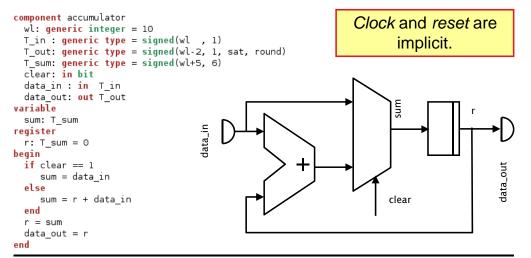

#### LANGAUGE FEATURES

- Explicit distinction between wires and registers.

- Implicit clock and reset.

- Generic data types allowing propagation of data types down hierarchy (e.g. floating-point to fixed-point refinement).

- Data types for DSP, especially fixed-point data types.

- Support for overflow and quantization modes.

- Efficient simulation of fixed-point data types.

- No semicolons!

- Simple: can be learned in one day!

#### RTL DESIGN WITH ARX

#### \_ maron o,

#### **ON-LINE FEATURES**

Please visit:

www.bibix.nl

- The website gives access to:

- On-line wiki-style manual,

- Web-based demonstration (upload Arx, download corresponding C++ and VHDL),

- An IP library of basic blocks: FIR filter, CORDIC, FFT, etc.

- A GFSK receiver.

- Feedback on Arx, requests for cooperation, very welcome.

© Sabih H. Gerez, University of Twente, The Netherlands

19

UT. RTL DESIGN WITH ARX

IMPLEMENTATION OF DSP

March 9, 2018

#### **EXAMPLE: COMPONENT INSTATIATION**

```

# subcomponent

component req

word length: generic integer = 8

: generic type = bitvector (word length)

data in

: in T IO

component top

data out : out T IO

word length: generic integer = 12

: generic type = bitvector (word length)

: in T topIO

data in

register

data out : out T topIO

storage : T IO = 0

variable

data internal: T topIO

storage = data in

data out = storage

r1: req

T IO - T topIO

data in => data in

data out => data internal

word length = word length

data in => data internal

data out => data out

# no functionality at this level

```

SIGN WITH ARX ■ March 9, 2018

THE ARX LANGUAGE: BUILDING BLOCKS

#### Components

- Same as entities (VHDL), modules (Verilog/SystemC)

- Contain sequential logic

- Can be instantiated inside other components (hierarchical descriptions are allowed)

- In current version: entire design in one file.

#### Functions:

- Contain only combinational logic

- In current version: not supported in VHDL generation (you need to write the VHDL function by hand)

© Sabih H. Gerez, University of Twente, The Netherlands

UT.

IMPLEMENTATION OF DSP

RTL DESIGN WITH ARX

March 9, 2018

20

#### **ARX DATA OBJECTS**

#### Registers:

- They store data are updated at the end of clock cycle.

- Assignment is concurrent.

#### Variables:

- Correspond to wires.

- Assignment is sequential ("single assignment" not required).

March 9, 2018

#### **DATA TYPES**

- Scalar types:

- bit

- boolean

- integer

- real

- Enumerated types (e.g. for state specification)

- Vector types:

- bitvector

- signed

- unsigned

© Sabih H. Gerez, University of Twente, The Netherlands

IMPLEMENTATION OF DSP

RTL DESIGN WITH ARX

March 9, 2018

23

#### **FIXED-POINT SUPPORT**

- Use of fixed-point data type implies automatic code generation for:

- Binary-point alignment

- Sign extension

- Handling of overflow and quantization mode.

#### FIXED-POINT DATA TYPES

Refinement of signed/unsigned:

IMPLEMENTATION OF DSP

- By supplying additional optional arguments for:

- Integer word length

- Overflow mode

- Quantization mode

- Examples:

- signed(8)

- unsigned(8, 3): fixed-point with 5 fractional bits, wrap-around for overflow, truncate for quantization

- unsigned(8, 3, saturate, round)

© Sabih H. Gerez, University of Twente, The Netherlands

IMPLEMENTATION OF DSP

March 9, 2018

RTL DESIGN WITH ARX

#### **EXAMPLE: USE OF CONSTANTS**

```

register

# three registers initialized with the same value

bvall: bitvector(8) = 0b10101010

bval2: bitvector(8) = 0haa

bval3: bitvector(8) = 170

# more examples of constants

bval4: unsigned(8) = 0haa

bval5: unsigned(8,2) = 1.75 # no loss of precision

bval6: signed(8,2) = -1.5 \# no loss of precision

bval7: signed(8,4) = 3.14 # will be converted to 3.125 = 50/16

```

IMPLEMENTATION OF DSP

March 9, 2018

### **EXAMPLE: ENUMERATION DATA TYPE**

```

type

input state = enum(start, processing, ready)

```

```

# a registered signal of type input state with its reset value

register

current state: input state = input state.start

# later on in the code

begin

if current state == input state.start

current state = input state.processing

```

© Sabih H. Gerez, University of Twente, The Netherlands

27

March 9, 2018

#### **EXAMPLE: CASE STATEMENT**

```

case output state

when out state.start

if start of processing

output state = out state.processing

end

when out state.processing

if end of processing

output state = out state.ready

end

else # default case; no action

end

```

March 9, 2018

#### **EXAMPLE: ARRAYS**

```

component top

T IO

: generic type = signed(10, 5, sat, round)

data in

: in T IO

data out

: out T IO

type

T enum: enum (one, two, three)

T ar1: array[3] of T IO

T ar2: array[3] of T enum

register

v1 : T ar1 = 0

v2 : T ar2 = {T enum.three, T enum.two, T enum.one}

v3 : array[5] of T IO = {5, 4, 3, 2, 1}

begin

v1[1] = data in

for i in 0:1

v2[i] = v2[i+1]

# example of accessing individual bits in an array of vectors

v3[0][0:4] = v1[2][5:9]

v3[0][5:9] = v1[2][0:4]

```

© Sabih H. Gerez, University of Twente, The Netherlands

RTL DESIGN WITH ARX

IMPLEMENTATION OF DSP

March 9, 2018

#### FOR STATEMENT

- Iteration based on an index variable

- Index can only be incremented by 1

- Specifies iteration in *space* not in *time* (as in e.g. VHDL).

- Example:

```

for i in 1:half size

delay group[i] = delay line[half size-i] + delay line[half size+i]

end

```

## RTL DESIGN WITH ARX

March 9, 2018

#### **CODE GENERATION**

- · Based on data-flow analysis & static scheduling.

- C++-code generation (targeted for fast simulation):

- Flattens description

- Maps fixed-point data types on integers (limited to 64 bits)

- C++ object with:

- reset method

- run method to simulate one clock cycle

- Optional VCD generation for waveform viewing (now: all or none)

- VHDL-code generation (targeted for synthesis):

- Preserves component hierarchy

| RTL DESIGN WITH ARX |         |

|---------------------|---------|

|                     | SUMMARY |

- A domain-specific language for the RTL MoC, e.g. Arx, bridges wall when descending from the system level.

- Arx brings about that one source code generates:

- C++-based simulation model optimized for simulation speed

- VHDL code for synthesis.

- The Arx approach:

- Saves manual recoding time!

- Is correct by construction!

© Sabih H. Gerez, University of Twente, The Netherlands

© Sabih H. Gerez, University of Twente, The Netherlands